On November 22, the award ceremony for the 22nd Korea Semiconductor Design Competition was held at COEX, Seoul. PhD students Yoonseo Cho, Suneui Park, and Jooeun Bang from Professor Jaehyouk Choi’s laboratory from the School of Electrical Engineering received the Presidential Award. The team developed an ultra-low-noise W-band phase-locked loop (PLL), a control system that generates an output signal of phase related to its input signal, to be used for efficient 6G communication.

The annual competition is held jointly by the Korea Semiconductor Industry Association and the Ministry of Trade, Industry and Energy. It aims to cultivate creative ideas and design skills of university students in the field of semiconductor design as well as encourage cooperation between researchers at universities and the industry. The only competition in Korea of its kind, participants are required to simulate and implement their ideas with semiconductor chips. The submitted works were assessed based on four criteria: creativity of the topic and method of design, technological level of difficulty and performance, feasibility of commercialization, and the completeness of the design.

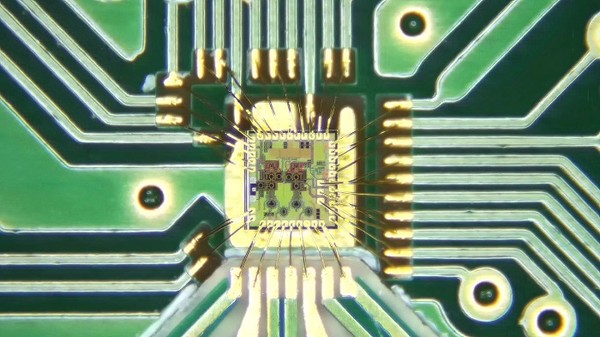

The mobile communication module presented by the team was based on the W-band PLL, which uses a frequency bandwidth of 75 – 110 GHz to generate the output signal. A high frequency of over 100 GHz is desirable to achieve the broad communication bandwidth required for the extremely rapid transmission of data aimed for in 6G telecommunications. However, the conventional complementary metal-oxide-semiconductor (CMOS) process utilized to fabricate the semiconductor chips has previously had limitations in noise performance and creating accurate reference signals at high frequencies. The research team overcame these limitations by achieving ultra-low-noise signals at these high frequencies using CMOS for the first time. This meant that interference to communication was substantially removed, and high-order modulation and demodulation of signals was made possible. Considering the advantages of the CMOS method in small, low-power design, it is expected that the results from the award-winning team will contribute to the efficiency and price competitiveness of 6G telecommunication chips that will likely be widely used in the near future.